第四章 存储系统

cache存储器

重点与难点

- 存储系统层次结构和评价方法

- 半导体存储器的组织

- Cache存储系统的基本原理与实现方式

- 虚拟存储系统

4.1 存储器的分类

按存储介质

- 半导体

- 磁性材料

- 光

- 纸

按存储方式分:

-

随机存储器:可按地址访问且访问时间与单元的物理位置无关

- 顺序存储器 :存储时间与单元的物理位置有关

- 磁盘:半顺序和半随机设备

按信息的可保存性

- 永久性: 与是否断电无关

- 非永久性:断电后信息消失

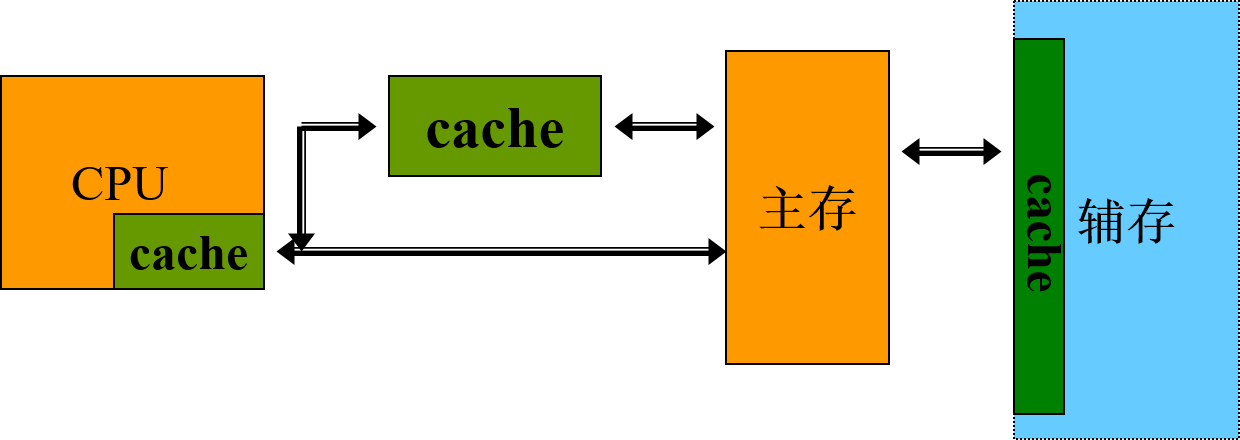

按在计算机系统中所起的作用

-

控制存储器(CM or CS)

-

CPU中的Cache

-

CPU 外面的 Cache

-

主存

-

辅存

4.2 计算机分级结构

- CPU

- CACHE

- 主存

- 辅存

4.3 半导体存储器

-

静态MOS存储器(SRAM)

-

动态存储器(DRAM)

-

只读存储器

4.4 信息存储及存储器编址

4.5 存储器扩展及综合运用

需要连接的线:地址线、数据线、读 / 写控制线、片选信号

片选可以理解成选片,很多芯片挂在同一总线上的时候,需要有一个信号来区别总线上的数据和地址由哪个芯片处理,这时就需要一个片选信号CS(chip select),一般是在划分地址空间时,由逻辑电路产生的。在数字电路设计中,一般开路输入管脚呈现为高电平,因此片选信号绝大多数情况下是一个低电平。

- 位扩展 :当数据位不足时

-

字扩展 :当容量不足时

- 字位同时扩展:当数据位和存储体的容量均不足时使用

位扩展

-

数据位不够时位扩展

-

所需芯片数量:K= 数据线位数/ 存储体数据位

字扩展

- 容量不够时字扩展

- 所需芯片数量:L= 主存容量/ 存储体容量 或: L= 2^(CPU地址线数 - 存储体地址线数)

字位同时扩展

-

当用户所需要的存储器的容量和数据位均大于存储体的容量和数据位时,采用字位同时扩展。

-

所需要的存储体的数量:P = K × L =存储器的容量×数据位 / 存储芯片的容量×数据位

4.6 高速存储器

快的原因

- 没有刷新

- 没有预充

双端口存储器

-

具有相互独立的两组读/写控制电路, 正常情况下各自独立进行读/写

-

左右读/写不同单元时不发生冲突

-

同时存取同一个单元时,发生读写冲突。此时由判断逻辑来延时一个读写控制器的工作并设该端口

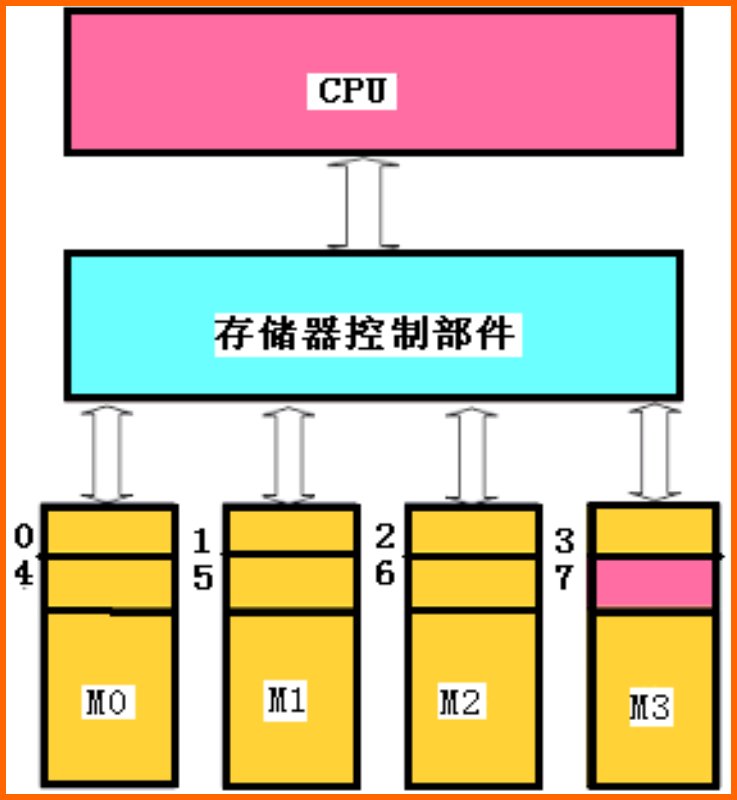

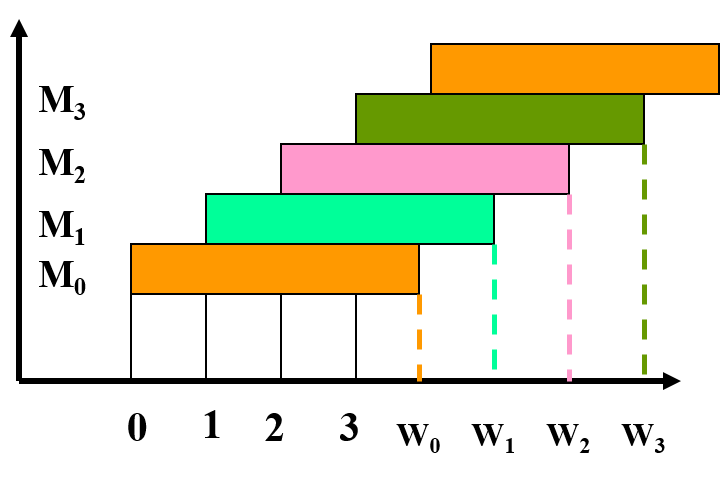

多体交叉存储器组织

-

增加了存储器控制部件

-

总线宽度不变

-

四个存储器的容量相同,各有自己的读\写线路、地址寄存器、数据寄存器

-

各模块的读写过程将重叠进行,对于每个模块而言,读写时间不变,但对CPU而言,在一个存储周期内连续访问四个模块

-

是一种并行存储器结构

-

实现存储并行访问的数据放置策略

- 顺序放置

- 数据交叉放置

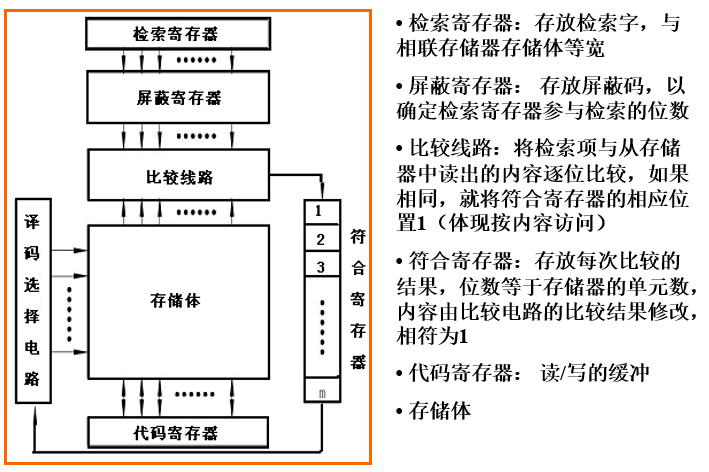

相联存储器:按内容访问的存储器

-

能实现快速查询

-

组成: